TR-O-0124

29

ミリ波帯多層化MMICの研究

今岡 俊一

1996. 3.15

ATR光電波通信研究所

# 目次

| 1 | まえがき                                                                                                                                                                     | 1                                |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 2 | 多層構造による受動回路         2.1 基本構造          2.2 薄膜伝送線路          2.3 積層化方向性結合器          2.4 抵抗                                                                                  | 2<br>2<br>2<br>3<br>4            |

| 3 | トランジスタ         3.1 基準面                                                                                                                                                   | 20<br>20<br>20<br>20             |

| 4 | ミリ波帯平衡型増幅器         4.1 回路構成                                                                                                                                              | 29<br>29<br>29<br>30             |

| 5 | SPDT スイッチ         5.1 回路構成       .         5.2 試作結果       .         5.2.1 SPDT スイッチ       .         5.2.2 移相器       .         5.2.3 入出特性       .         5.3 まとめ       . | 35<br>35<br>35<br>36<br>36<br>36 |

| 6 | スタック IC         6.1 構造と特徴          6.2 試作 MMIC          6.2.1 回路構成          6.2.2 試作結果          6.3 まとめ                                                                  | 45<br>45<br>45<br>45<br>46<br>46 |

| 7 | あとがき                                                                                                                                                                     | <b>52</b>                        |

| 8 | 参考文献                                                                                                                                                                     | 53                               |

#### 1 まえがき

モノリシックマイクロ波集積回路 (MMIC) は、無線装置等の小型化・低価格化を図る有力な回路技術として各方面で積極的な研究開発が行なわれている。 ATR 光電波通信研究所では、MMIC の超小型化を目的として、GaAs 基板表面に金属・誘電体薄膜を積層し、伝送線路として機能させる多層化 MMIC を提案、検討がなされてきた [1]-[13]。多層化 MMIC では伝送線路の小型化・線路交差・線路変換が容易にできるほか、線路を積層化した回路構成も可能で、新しい回路構成の実現や設計性の向上が図れる。しかしながら、その適用周波数帯はマイクロ波帯 (~30 GHz) が中心で、移動通信のマルチメディア化に対応して近年注目されているミリ波帯への適用例は少ない [13]。特に増幅器等の能動回路に多層化 MMIC を適用した例は無かった。そこで本研究では、ミリ波帯で動作する小型・高機能 MMIC を多層化 MMIC により設計・試作し、得られた特性と設計性から、その有効性を確認する。

本報告は、まず基本となる多層化 MMIC による薄膜伝送線路のミリ波特性 ( $\sim$ 60 GHz) について述べ、次に回路構成上で重要な役割を有する方向性結合器について、既に提案されている積層化方向性結合器 [10]-[11] のミリ波帯 (50 GHz) への適用結果を述べる。これら受動回路について述べた後、能動回路を構成する上で不可欠なトランジスタの取り扱いについて述べる。次にこれらの情報を元にして設計・試作したミリ波帯平衡型増幅器、及び SPDT スイッチについて述べる。また、MMIC チップを縦方向に積層するスタック IC の提案を行ない、この IC に適用可能な構造を持つミリ波帯増幅器の試作結果について述べる。

#### 2 多層構造による受動回路

#### 2.1 基本構造

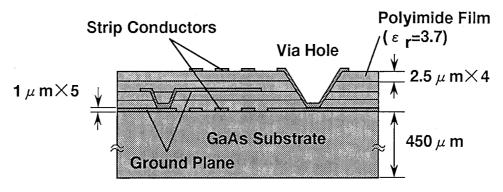

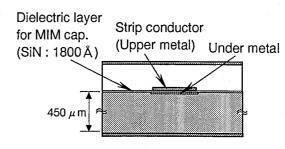

試作した MMIC の多層構造は、図 2.1-1 に示すように  $2.5\mu m \times 4$  層のポリイミド薄膜 (誘電率= 3.7) と膜厚  $1\mu m$  の金導体 5 層からなっている。また、特に除去しなければ GaAs 基板表面上に MIM 容量の誘電体として設けた 1800 A の SiN 膜(誘電率= 6.4)の上に第一の導体が形成される。

以下、本多層構造の特徴を利用した薄膜伝送線路と積層化方向性結合器について、次いで抵抗について述べる。

#### 2.2 薄膜伝送線路

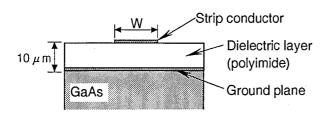

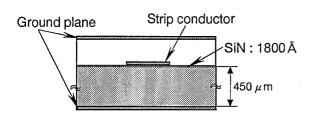

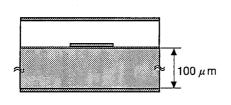

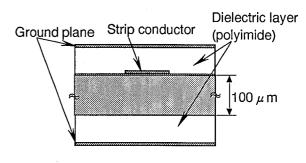

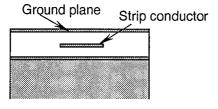

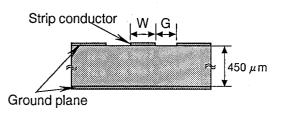

図 2.2-1 に多層化 MMIC による薄膜伝送線路の構造例を示す。 (1), (2) は最も基本的なマイクロストリップ線路 (MSL:Micro-Strip Line) で、各々 10, 7.5 $\mu$ m のポリイミド薄膜を介してストリップ導体を設けている。 (3)~(6) はポリイミド薄膜上に接地導体を配置し、 GaAs 基板上にストリップ導体を設けた逆マイクロストリップ線路 (IMSL:Inverted Micro-Strip Line) で、 (3)、 (4) は GaAs 基板厚 450 $\mu$ m 上にストリップ導体を設け、 (4) では (3) の構造に、 MIM 容量を併せ持つように 1800 Åの SiN 膜を介して下層導体を付加した構造である。 (5),(6) は、本報告で述べるスタック IC に適用する場合に考えられる構造で、 GaAs 基板厚を 100 $\mu$ m と薄くして基板を貫通するヴィアホールを可能とした構造で、 (6) では更に裏面にも多層配線を行なう場合を考え、ポリイミド層を設けている。 (7) はストリップ導体の上下にポリイミド層を介して接地導体を配置したトリプレート線路 (TPSL:Tri-Plate Strip Line) の構造を示している。 最後に (8) は比較のために用いるコプレナー線路の構造を示す。

これらの構造を有する線路の特性インピーダンス,及び実効誘電率は準 TEM 近似の有限要素法を用いた静電場解析により、導体損は有限要素法を用いて求め、表 2.2 にまとめて示す。また、特性インピーダンス  $50\Omega$  の線路についてはその挿入損失の実測結果も併せて示す。

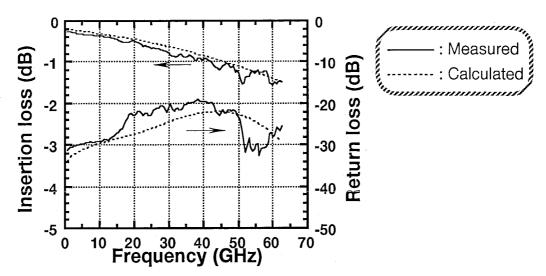

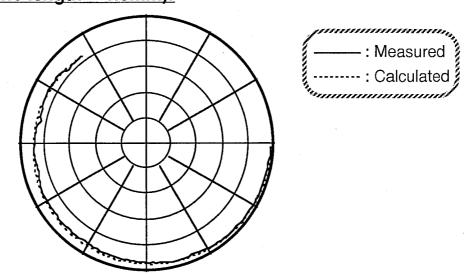

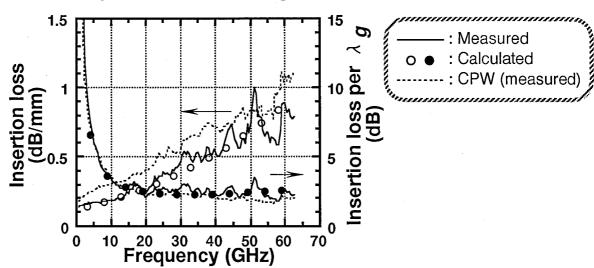

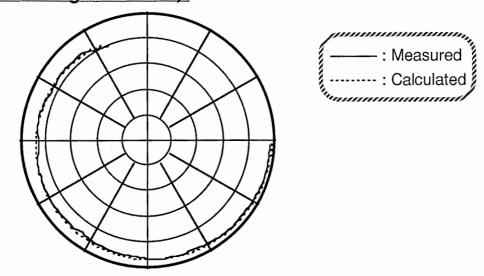

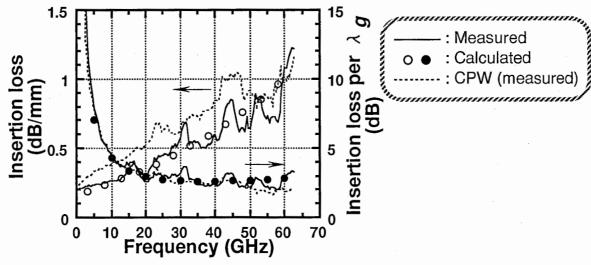

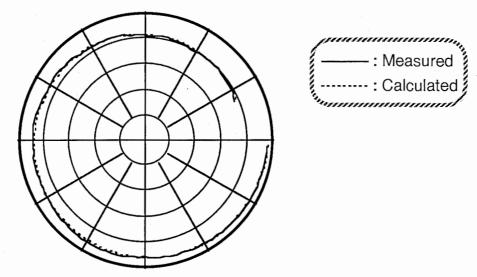

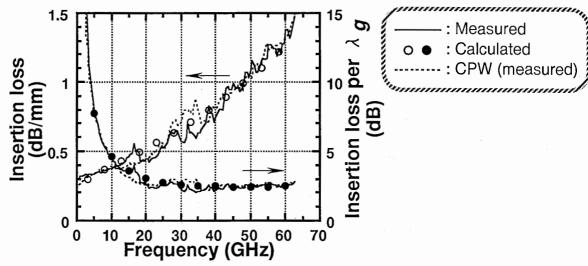

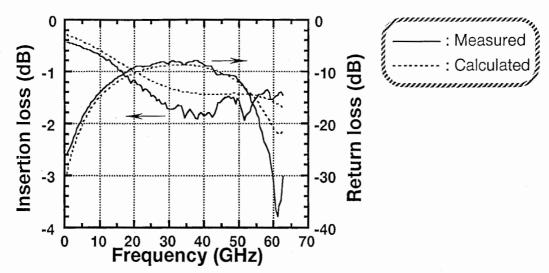

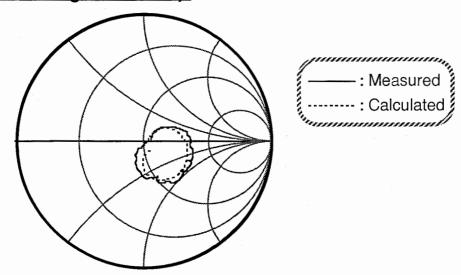

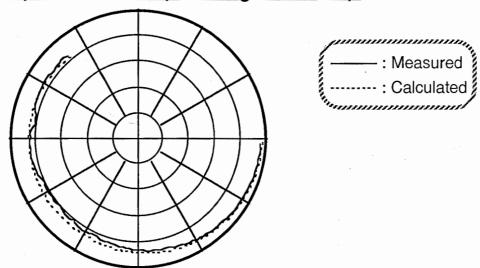

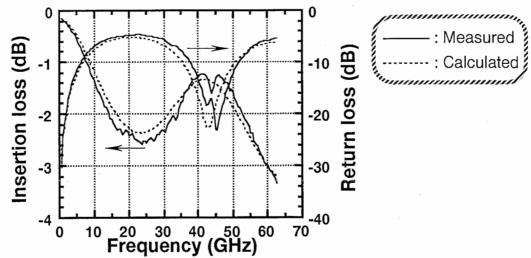

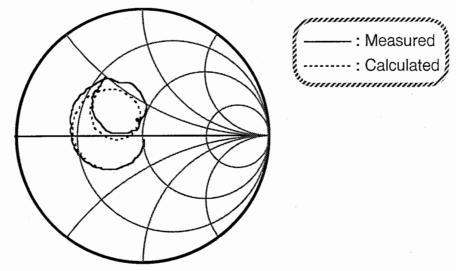

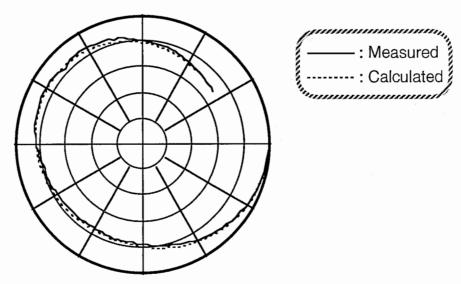

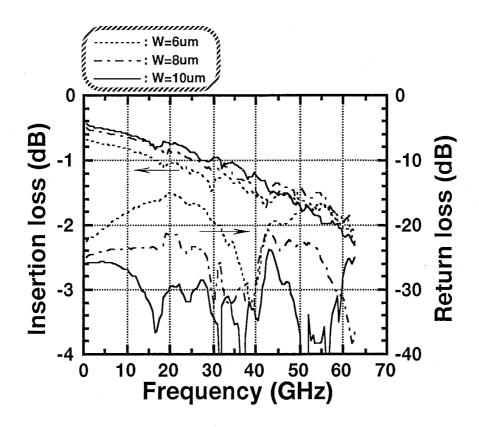

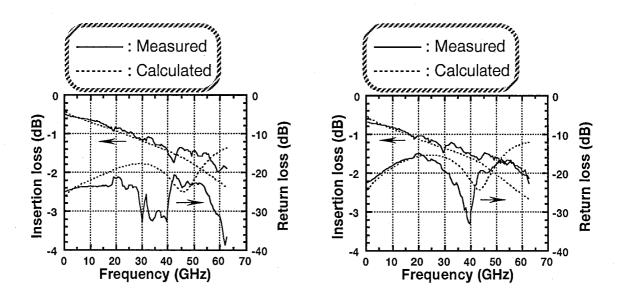

まず、特性インピーダンス  $50\Omega$  の線路について、同じストリップ導体幅を有するコプレナー線路と比較して述べる。図 2.2- $2\sim4$  に各々、図 2.2-1 の (1), (2), 及び (3) の構造を持つ線路  $(Zo=50\Omega)$  についてまとめる。各図の (a) に挿入損失と反射損失の、(b) に極座標表示で透過係数 S21 の実測・計算結果を比較して示す。各線路共に反射損失は周波数 60 GHz まで 20 dB 以上が得られており、実測・計算結果も良く一致している。また、各図の (c) には単位長あたり、及び波長あたりの挿入損失を、同じストリップ導体幅を有するコプレナー線路の実測結果と比較して示す。コプレナー線路と比較して、(1),(2) のマイクロストリップ線路の実効誘電率は 3 前後と小さいため、即ち波長短縮率が小さいために波長あたりの挿入損失は大きく回路設計上不利である。しかし、(3) の逆マイクロストリップ線路では、波長あたりの挿入損失はコプレナー線路とほぼ同程度で、配線密度の点ではストリップ導体の両側に接地導体を配置する必要の有るコプレナー線路と比べて有利であると考える。尚、各線路共に 20 GHz 以上の周波数域では波長あたりの挿入損失はほぼ一定であり、ミリ波以上の周波数域でも十分に使用できると考える。

次に  $50\Omega$  以外の線路について述べる。図 2.2-5, -6, -7 に各々、特性インピーダンス  $73\Omega$  のマイクロストリップ線路、 $25\Omega$  の逆マイクロストリップ線路、及び  $21\Omega$  のトリプレート線路の実測・計算結果を比較して示す。両者は各線路共に良く一致している。

最後に逆マイクロストリップ線路に関して、他の線路と異なる点について述べる。図 2.2-1 の (1), (2), (7) で示すマイクロストリップ線路、及びトリプレート線路では GaAs 基板とストリップ導体間には接地導体が存在し、 GaAs 基板は単なる支持基板として機能している。しかしな

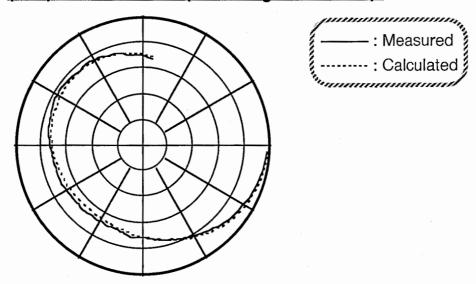

がら、逆マイクロストリップ線路ではストリップ導体が GaAs 表面上に配置されている。今回の試作に用いた構造では、 2.1 基本構造で述べたように特に除去しなければ GaAs 基板表面上に設けた MIM 容量の誘電体の上に第一の導体が形成される。当初、この SiN 膜がどの程度、線路の特性に影響するか未知であったため、ストリップ導体幅を 6, 8,  $10\mu m$  と変えた場合の TEG を作製、その実測・計算結果で比較を行なった。 3 線路共に  $50\Omega$  に近い特性を示すが、実測結果では図 2.2-8 に示すように導体幅  $10\mu m$  で挿入・反射損失共に  $50\Omega$  に最も近い結果が得られた。準 TEM 近似の有限要素法を用いた静電場解析においては、この結果は SiN 膜を考慮しなければ得られず、考慮しなければ導体幅  $7\mu m$  でほぼ  $50\Omega$  となる。線路幅はマスク寸法で述べているが、その作製精度は  $\pm 5\%$  以内と考えられるため、マスク寸法と実寸法の差では説明しきれない。また、ポリイミド膜厚についても同様である。これらの結果より、逆マイクロストリップ線路の特性計算においては、 SiN 膜を考慮すべきであると言える。尚、表 2.2 に示す逆マイクロストリップ線路の計算結果は全て SiN 膜を考慮した値で、図 2.2-4, -9 に示すように実測・計算結果は良く一致している。

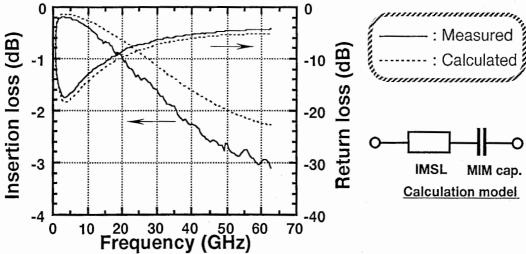

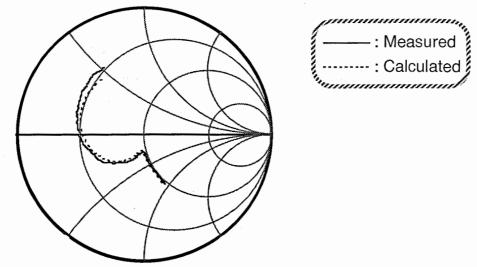

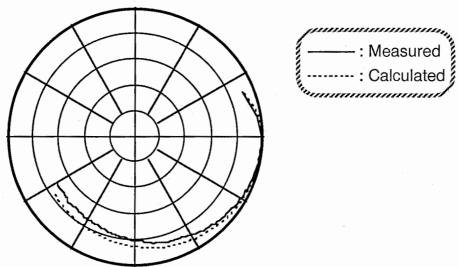

次に MIM 容量を併せ持つ逆マイクロストリップ線路について述べる。図 2.2-10 はその実測・計算結果の比較を示す。計算における線路の特性インピーダンス、実効誘電率、及び導体損の値は、表 2.2 の (3)-2 の下層導体の無い構造の値を用い、容量の考慮は集中定数的に容量を直列接続した。数千  $^{A}$  の下層導体に電流集中するため損失は大きくなっているが、線路と MIM 容量を兼ねても支障はない。

尚、写真 2-1 に評価した伝送線路の外観写真を示す。

#### 2.3 積層化方向性結合器

90 度合成・分配器として、ブランチラインハイブリッド、及び方向性結合器はマイクロ波回路を構成する上で重要な役割を有している。しかし、MMICへの適用はその占有面積や結合度の観点から難しかった。これを解決する手段として多層化 MMIC の構成を用いた方向性結合器やハイブリッドリングの報告もなされているが [2]–[9]、その占有面積は低減したものの、回路損失が大きくなる問題が残された。しかし近年 ATR では、これらの問題を解決するため新たに多層構造の特徴を活用した積層化方向性結合器を提案し [10]–[11]、ミリ波帯  $(40~{\rm GHz})$  無限移相器等に適用してきた [13]。

ここでは、先に提案されている積層化方向性結合器を 50 GHz 帯に適用し、その特性と設計性について述べる。

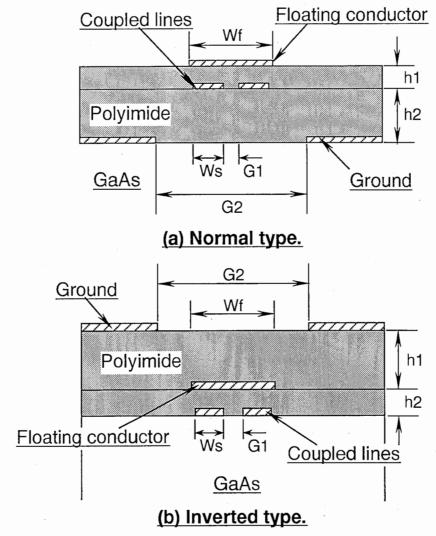

図 2.3-1 に多層構造による (a) Normal type, (b) Inverted type 2 種類の方向性結合器の断面 図を示す。結合したマイクロストリップ上に誘電体層を介して浮遊導体を設け、さらに接地導体 にギャップを設けている。本構造を用いることにより、 3dB 程度の強い結合度を得るために必要 な高い偶・奇モード特性インピーダンス比が得られる。図 2.3-1 において、 Ws はマイクロストリップ導体の幅、 Wf は浮遊導体の幅、 G1 はマイクロストリップ導体間のギャップ、 G2 は接地 導体に設けられたギャップであり、 h1、 h2 は、各々ポリイミドの膜厚である。表 2.3 に各々の タイプの結合度 3dB,入出力インピーダンス  $50\Omega$  の積層化方向性結合器の構造諸元と有限要素法で求めた各モードの特性値をまとめて示す。

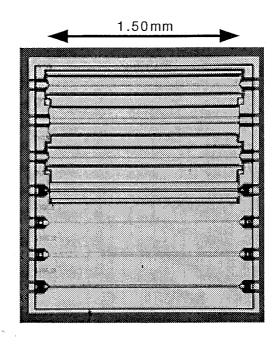

中心周波数  $50 \mathrm{GHz}$  の  $3 \mathrm{dB}$  方向性結合器を各タイプで試作、評価した。チップの外観写真を写真 2-2 に示す。結合長(1/4 波長)は、偶・奇モード時の管内波長が異なるためにこれらの平均値を用いて求め、(a) Normal type, (b) Inverted type 各々  $720 \mu\mathrm{m}$ ,  $600 \mu\mathrm{m}$  となった。尚、回路の小型化を計るためにメアンダ形状のパターン配置とし、入出力端は引出し線路、及びコンタクトホールを介してプロービング用のコプレーナ線路に接続されている。

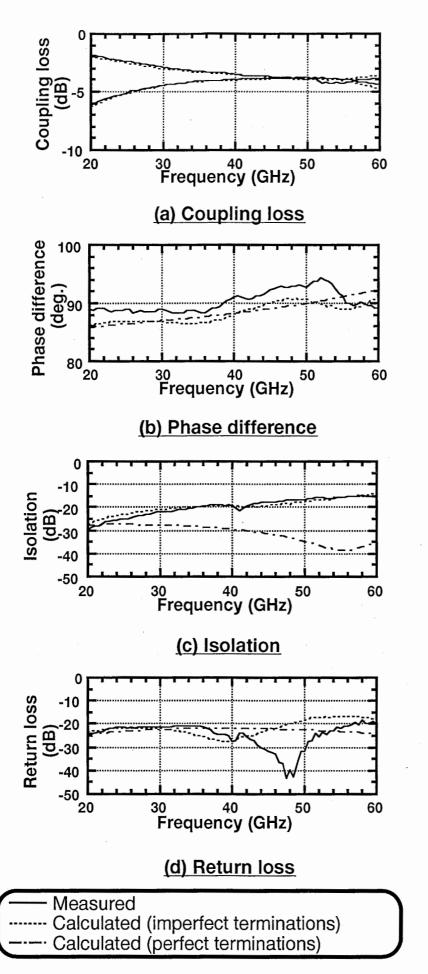

図 2.3-2 に試作した Normal type の 3dB 方向性結合器の周波数特性を示す。評価はネットワークアナライザとウェハプローブにより行ない、4端子の内、評価端子以外の 2端子には  $\sim$ 55GHz で 14dB 以上のリターンロスを有する終端プローブを接続した。図にはこの不完全な終端プローブ特性を用いた場合と完全な終端を用いた場合の計算結果を併せて示す。  $45\sim$ 55GHz の周波数帯域で結合度 3.9dB $\pm 0.3$ dB 以内、カップリング及びスルーポート間の位相差  $93^{\circ}\pm 2^{\circ}$  以内が得られた。また、 $0\sim$ 55GHz の範囲で入出力リターンロス 21dB 以上、及びアイソレーション 14dB 以上を得た。尚、実測結果と不完全な終端を考慮した計算結果は非常に良く一致しており、完全な終端を接続した場合の本来のアイソレーションは 30dB 以上あると考えられる。

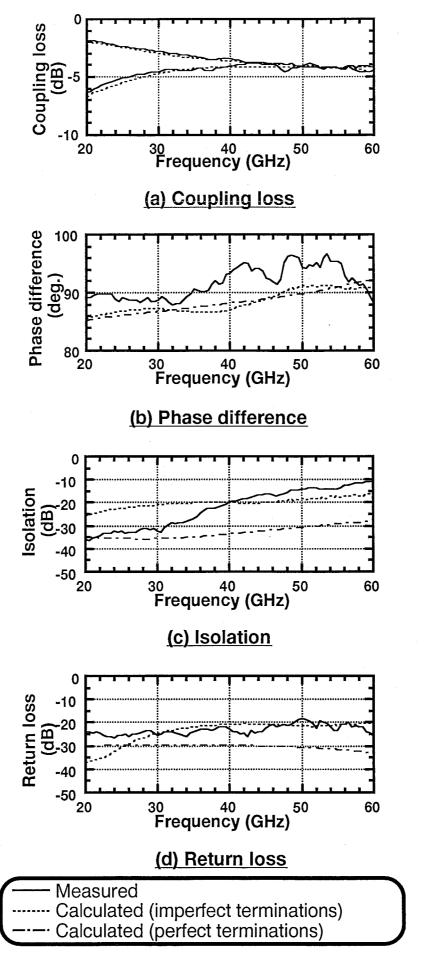

図 2.3-3 に試作した Inverted type の 3dB 方向性結合器の周波数特性を示す。実測結果では  $45\sim55$  GHz の周波数帯域で結合度 4.0 dB $\pm0.5$ dB 以内、カップリング及びスルーポート間の位相 差  $94^\circ\pm4^\circ$  以内が得られた。また、 $0\sim55$  GHz の範囲で入出力リターンロス 19dB 以上、及びアイソレーション 14dB 以上を得た。

#### 2.4 抵抗

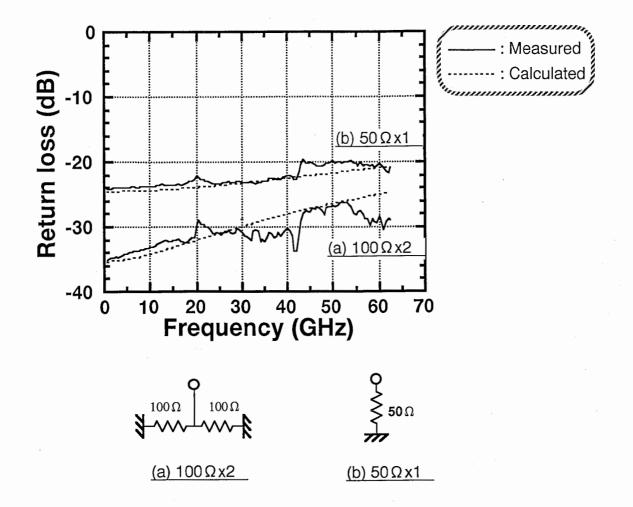

前項で述べたが、終端抵抗の特性は方向性結合器のアイソレーション特性等、組み合わせて用いる受動回路の特性に影響する。本試作では GaAs 表面のエピ層で形成するメサ抵抗を用いている。周波数上昇に伴い、大きさを持つ抵抗部とその引き出し部の形状により特性は異なる。ここでは、写真 2-3 に示すように (a) コプレナー線路の先端に  $100\Omega$  の抵抗 2 個で並列に接地した場合と、(b)  $50\Omega$  の抵抗 1 個で接地した場合との特性比較を行なった。 DC 抵抗値は (a) で約  $52\Omega$ , (b) で約  $56\Omega$  で、メサ部の縦横比で決まる抵抗値において、その比に対して敏感でない高抵抗 2 個を用いた方がより  $50\Omega$  に近い値となった。次に各々の反射特性を図 2.4 に示す。 (a) の形状の方が 50 GHz で約 6 dB 程度良好な特性が得られていが、この差は DC 抵抗の値によるものであると考えられる。次に周波数特性の傾きに着目する。大きさを持たない集中定数的な抵抗のみを考えると、その傾きはゼロとなるが、図 2.4 では (a), (b) 共に傾きを有しており、(b) の方がその傾きは小さい。これは引き出し部も含めた形状を反映していると考えられ、さらに高い周波数になれば (a), (b) が逆転すると予想できる。

結論的には DC 抵抗値をより精度良く作製することと、引き出しを含めた抵抗部の形状で不連続部を極力減らし、抵抗部と接地導体間で寄生成分を生じさせないことが重要であると考える。尚、写真 2-4-(c) は  $1.2 \mathrm{K}\Omega$  の抵抗で、 DC 抵抗の実測値は約  $1.3 \mathrm{K}\Omega$  であった。

Fig. 2.1-1 Basic structure of multilayer MMIC.

(1) Microstrip line

(2) Microstrip line on middle layer

(3) Inverted microstrip line

(4) Inverted microstrip line with MIM capacitor

(5) Inverted microstrip line

(Thickness of GaAs wafer = 100 \(\mu\), m, polyimide layer on single side)

(6) Inverted microstrip line

(Thickness of GaAs wafer = 100  $\mu$  m, polyimide layer on both sides)

(7) Triplate line

(8) Coplanar waveguide

Fig. 2.2-1 Configurations of thin film transmssion lines.

Table 2.2 Structural parameters and characteristics of thin film transmission line.

|                       | Structure              | Line width ( $\mu$ m)     | Polyimide<br>thickness<br>( $\mu$ m) | Calculated re                 | esults by FEM                       | Measured results (at 50GHz) |                           |                                          |

|-----------------------|------------------------|---------------------------|--------------------------------------|-------------------------------|-------------------------------------|-----------------------------|---------------------------|------------------------------------------|

| Туре                  |                        |                           |                                      | Characteristics impedance (Ω) | Effective<br>dielectric<br>constant | Conductor loss<br>(dB/mm)   | Insertion loss<br>(dB/mm) | Insertion loss<br>per wavelength<br>(dB) |

|                       | (1) - 1                | 10                        | 10                                   | 73.1                          | 2.71                                | 0.337                       |                           |                                          |

| Microstrip line       | (1) - 2                | 20                        | 10                                   | 50.9                          | 2.84                                | 0.298                       | 0.71                      | 2.5                                      |

|                       | (2)                    | 14                        | 7.5                                  | 50.2                          | 3.16                                | 0.413                       | 0.80                      | 2.7                                      |

|                       | (3) - 1                | 10                        | 10                                   | 50.7                          | 6.48                                | 0.650                       | 1.10                      | 2.6                                      |

|                       | (3) - 2                | 42                        | 10                                   | 25.6                          | 5.33                                | 0.435                       |                           |                                          |

| Inverted              | (3) - 3                | 8                         | 10                                   | 54.2                          | 6.71                                | 0.719                       |                           |                                          |

| microstrip line       | (3) - 4                | . 6                       | 10                                   | 57.8                          | 6.98                                | 0.836                       |                           |                                          |

|                       | (4)<br>(with MIM cap.) | Upper /Under<br>= 42 / 48 | 10                                   |                               |                                     |                             |                           |                                          |

|                       | (5)                    | 8                         | 10                                   | 48.9                          | 7.10                                | Thickness of GaAs           | Polyimide layer           | on single side                           |

|                       | (6)                    | 8                         | 10                                   | 50.8                          | 6.77                                | wafer = 100 μm              | Polyimide layer           | s on both side                           |

| Triplate line         | (7)                    | 18                        | 10                                   | 21.1                          | 3.70                                | 0.771                       |                           |                                          |

|                       | (8) - 1                | Width / Gap = 20 / 14     |                                      | 48.3                          | 6.67                                |                             | 0.88                      | 2.0                                      |

| Coplanar<br>waveguide | (8) - 2                | = 14 / 10<br>= 10 / 10    |                                      | 47.9                          | 6.56                                |                             | 1.00                      | 2.3                                      |

|                       | (8) - 3                |                           |                                      | 52.5                          | 6.53                                |                             | 1.10                      | 2.6                                      |

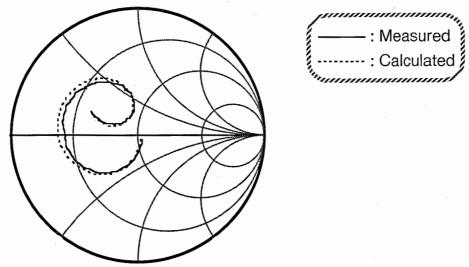

(a) Calculated and measured frequency characteristics (Line length = 1.5mm).

(b) Calculated and measured frequency characteristics (S21) in polar chart (Line length = 1.5mm).

(c) Measured losses per unit- and wave-length as compared with CPW having the same conductor width (W=20  $\mu$  m).

Fig. 2.2-2 Microstrip line (W=20  $\mu$  m, H=10  $\mu$  m).

(a) Calculated and measured frequency characteristics (Line length = 1.5mm).

(b) Calculated and measured frequency characteristics (S21) in polar chart (Line length = 1.5mm).

(c) Measured losses per unit- and wave-length as compared with CPW having the same conductor width (W=14  $\mu$  m).

Fig. 2.2-3 Microstrip line (W=14  $\mu$  m, H=7.5  $\mu$  m).

(a) Calculated and measured frequency characteristics (Line length = 1.5mm).

(b) Calculated and measured frequency characteristics (S21) in polar chart (Line length = 1.5mm).

(c) Measured losses per unit- and wave-length as compared with CPW having the same conductor width (W=10  $\mu$  m).

Fig. 2.2-4 Inverted microstrip line (W=10  $\mu$  m, H=10  $\mu$  m).

(a) Calculated and measured frequency characteristics (Line length = 1.5mm).

(b) Calculated and measured frequency characteristics (S11) in smith chart (Line length = 1.5mm).

(c) Calculated and measured frequency characteristics (S21) in polar chart (Line length = 1.5mm).

Fig. 2.2-5 Microstrip line (W=10  $\mu$  m, H=10  $\mu$  m).

(a) Calculated and measured frequency characteristics (Line length = 1.5mm).

(b) Calculated and measured frequency characteristics (S11) in smith chart (Line length = 1.5mm).

(c) Calculated and measured frequency characteristics (S21) in polar chart (Line length = 1.5mm).

Fig. 2.2-6 Inverted microstrip line (W=42  $\mu$  m, H=10  $\mu$  m).

(a) Calculated and measured frequency characteristics (Line length = 1.5mm).

(b) Calculated and measured frequency characteristics (S11) in smith chart (Line length = 1.5mm).

(c) Calculated and measured frequency characteristics (S21) in polar chart (Line length = 1.5mm).

Fig. 2.2-7 Triplate line (W= 18  $\mu$  m, H=10  $\mu$  m).

Fig. 2.2-8 Inverted microstrip line (W=6 / 8 / 10  $\mu$  m, H=10  $\mu$  m).

(a) W=8  $\mu$  m (Line length = 1.5mm). (b) W=6  $\mu$  m (Line length = 1.5mm).

Fig. 2.2-9 Inverted microstrip line (W=6 / 8  $\mu$  m, H=10  $\mu$  m).

(a) Calculated and measured frequency characteristics (Line length = 0.5mm).

(b) Calculated and measured frequency characteristics (S11) in smith chart (Line length = 0.5mm).

(c) Calculated and measured frequency characteristics (S21) in polar chart (Line length = 0.5mm).

Fig. 2.2-10 Inverted microstrip line with MIM capacitor (W=42 / 48  $\mu$  m, H=10  $\mu$  m).

Fig. 2.3-1 Cross-sectional view of directional couplers.

Table 2.3 Structural parameters and calculated characteristics of coupled section. The conductor losses are calculated at 50 GHz.

(a) Normal type.

|     |                               |        |       |          | 7~  | ,         | 75                       |                      |                |

|-----|-------------------------------|--------|-------|----------|-----|-----------|--------------------------|----------------------|----------------|

| St  | tructur                       | al par | amete | rs ( μ : | m)  |           | Calculated               | characteristics      |                |

| h1  | h2                            | Ws     | Wf    | Wf G1 G2 | G2  |           | Characteristic impedance | Effective dielectric | Conductor loss |

| 2.5 | 7.5                           | 15     | 44    | 10       | 110 |           | (Ω)                      | constant             | (dB/mm)        |

| Cou | Coupling length = $720 \mu$ m |        |       |          |     | Even-mode | 122.6                    | 4.66                 | 0.35           |

|     |                               |        |       |          |     | Odd-mode  | 20.9                     | 3.88                 | 1.12           |

## (b) Inverted type.

| St   | ructur  | al par | amete | rs (μ: | m)       |           | Calculated               | characteristics         |                |

|------|---------|--------|-------|--------|----------|-----------|--------------------------|-------------------------|----------------|

| h1   | h2      | Ws     | Wf    | G1     | G2       |           | Characteristic impedance | Effective<br>dielectric | Conductor loss |

| 7.5  | 2.5     | 10     | 34    | 10     | 120      |           | (Ω)                      | constant                | (dB/mm)        |

| Cour | oling l | enath  | = 60  | 0 μ m  | <u> </u> | Even-mode | 120.9                    | 6.45                    | 0.59           |

| •    | J       | Ü      |       | ,      |          | Odd-mode  | 21.0                     | 6.01                    | 1.56           |

Fig. 2.3-2 Measured and calculated characteristics of fabricated 3dB-coupler (Normal type).

Fig. 2.3-3 Measured and calculated characteristics of fabricated 3dB-coupler (Inverted type).

Fig. 2.4 Frequency characteristics of terminations.

写真 2 - 1 伝送線路

(a) Normal type

(b) Inverted type

写真 2 - 2 積層化方向性結合器

(a)  $100 \Omega x2$  (b)  $50 \Omega x1$  (c)  $1.3k\Omega$

写真2-3 抵抗

#### 3 トランジスタ

回路設計する上ではトランジスタの特性をどのように取り扱うかが重要となる。ここでは、まずトランジスタのSパラメータに関して、測定データをどのように補正して設計に用いるかについてを述べ、次により高い周波数域で動作させるのに適した電極形状について述べる。また、多層化 MMIC に特異なトランジスタ上部のポリイミド薄膜や接地導体の影響について述べる。

#### 3.1 基準面

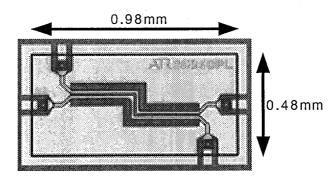

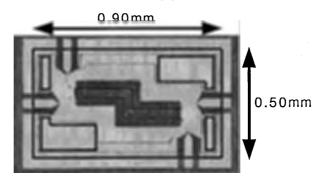

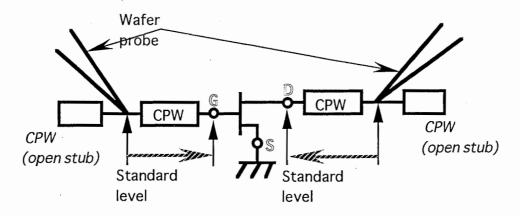

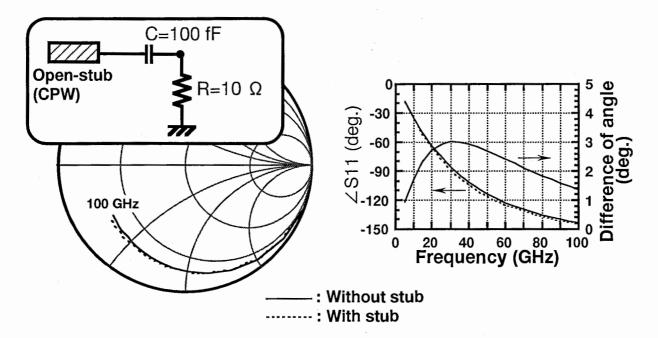

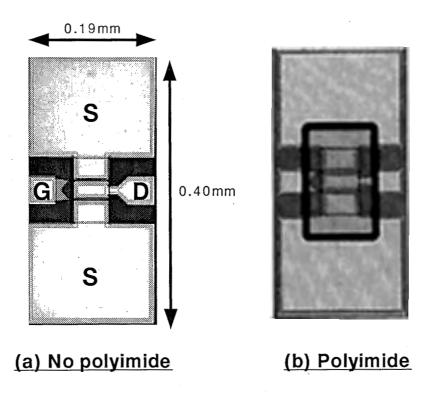

評価に用いるトランジスタ TEG の外観を写真 3-1, 2 に示す。ウェハプローブによる測定を行なうため、入出力端には特性インピーダンス  $50\Omega$  のコプレナー線路の引き出し電極を接続している。図 3.1-1 には TEG 測定時の状態を示すが、ウェハプローブの先端は引き出し電極のトランジスタ側の端面から数十  $\mu$ m 離れた所にオーバーラップして接触する。今回作製した TEG では、引き出し電極のコプレナー線路長は  $45\mu$ m で、測定時のオーバーラップは約  $30\mu$ m である。このオーバーラップする線路はオープンスタブとして働き、補正する必要がある。この影響をトランジスタの入力特性で調べる。図 3.1-2 の回路図で示すように、その入力特性を簡単のため抵抗、容量のみを接地することで表現し、端面に長さ  $30\mu$ m コプレナー線路のオープンスタブを接続する。このスタブの有無で  $1\sim3^\circ$  程度、反射位相差が見られる。

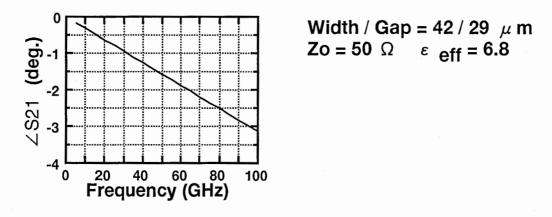

この補正を行なった後、基準面をウェハプローブ接触点からトランジスタ側の入出力端に移動する方が、回路設計時に考え易く、性能指数 (ft, fmax) の見積もりにおいても適当と考える。ここでコプレナー線路  $10\mu m$  あたりの透過位相は、図 3.1-3 に示すように 60 GHz で約  $2^\circ$  となる。尚、以後は上記補正を行なったデータを用いる。

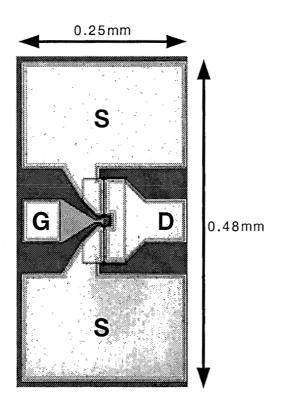

#### 3.2 電極形状

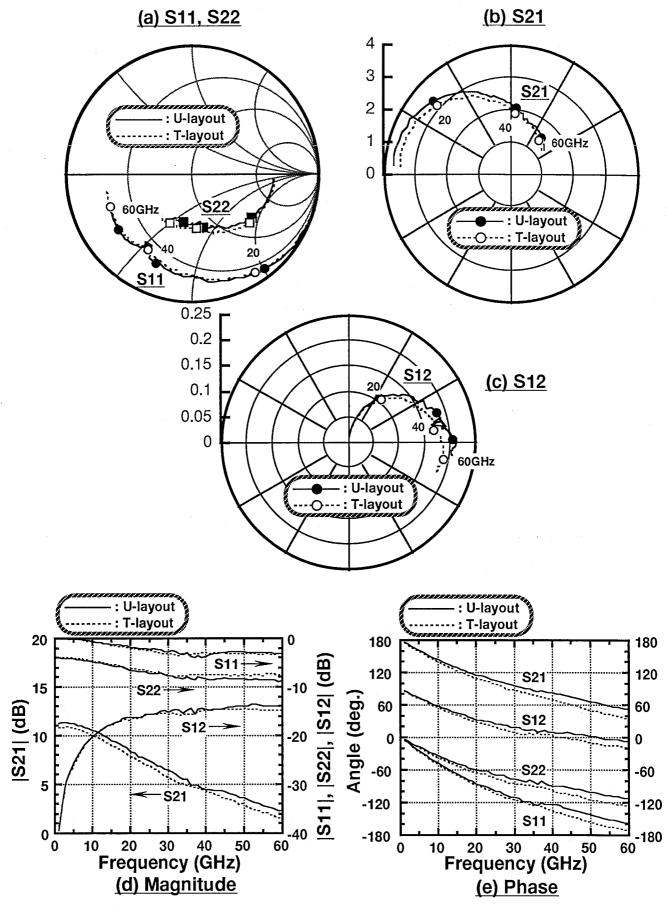

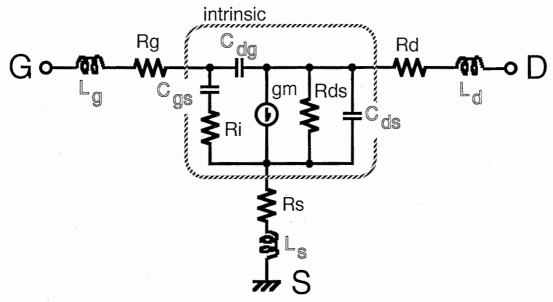

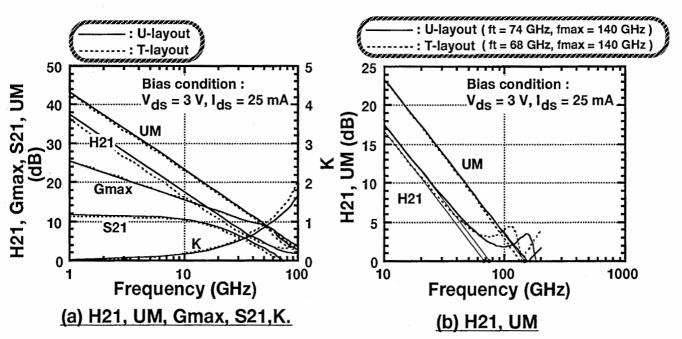

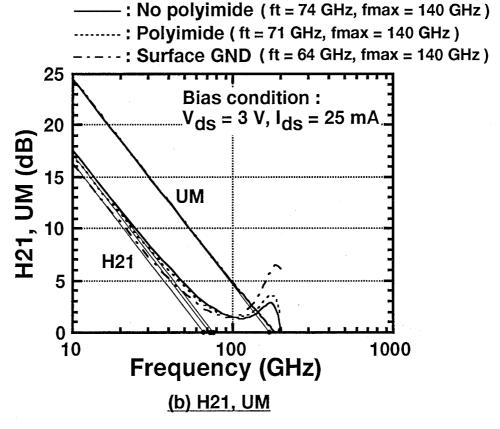

同一のウェハプロセスで作製したトランジスタにおいても、写真 3-1, 2 に示す U型( $\pi$ 型)、T型と異なる電極形状を持つ場合、その特性は異なる。図 3.2-1 はウェハ面内で近接し、DC 特性の一致する両電極形状の S パラメータ測定結果を比較している (本報告のトランジスタ特性は全てゲート幅  $100\mu m$  のものを用いている)。絶対値に関しては、順方向透過特性(S21)でその差は顕著で、 $50 \mathrm{GHz}$  で約  $1 \mathrm{dB}$  T型の方が小さい。また、位相回りでは全てのパラメータでT型の方が大きい。この測定結果と図 3.2-2 の等価回路を用いて求めた各定数を表 3.2 に示す。パラメータフィッテイングでは等価回路内のリアクタンス成分のみ電極形状により独立して、それ以外は両形状で等しい値を用いた。表で示すように入出力のリアクタンス成分で、T型が大きくなっているのが分かる。求めた等価回路定数を用いて  $200 \mathrm{GHz}$  まで外挿し、性能指数を求めた結果を図 3.2-3 に示す。図中 (b) で  $10 \mathrm{Hz}$ 1 の高周波側で  $10 \mathrm{Hz}$ 2 の方が大きくずれて見えるのは入出力のリアクタンスによる。  $10 \mathrm{fm}$ 2 に振むいが、 $10 \mathrm{fm}$ 3 に新し、 $10 \mathrm{fm}$ 4 に指数を求めた結果

以上の結果から、試作回路には高周波動作に有利な U 型電極形状のトランジスタを用いた。

## 3.3 上部ポリイミド薄膜、及び接地導体の影響

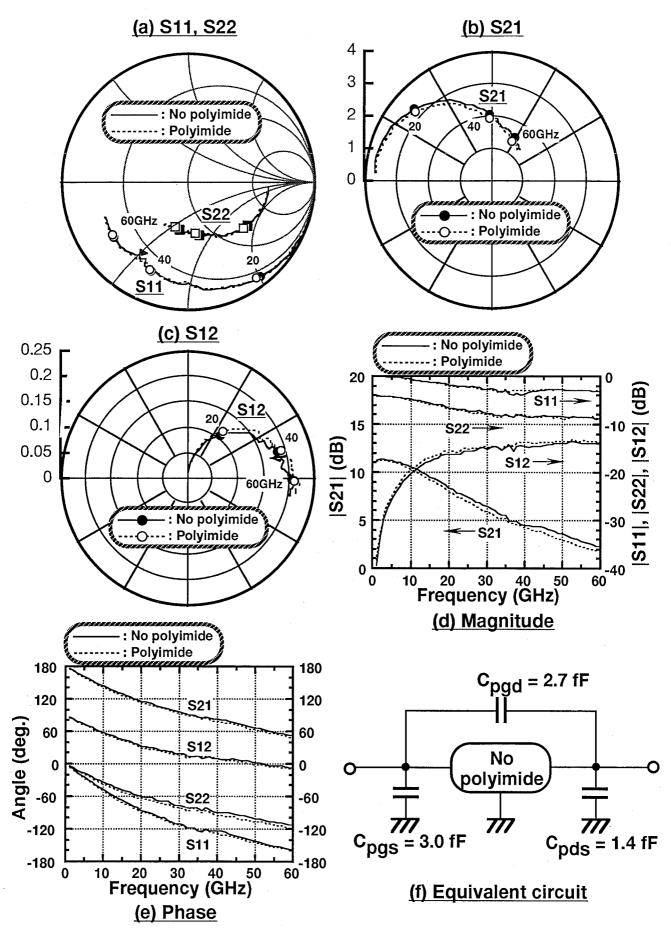

トランジスタ上部のポリイミド薄膜の影響を写真 3-1-(b) で示す TEG を評価・比較することで行なった。本 TEG は引き出し電極部を除いてポリイミド薄膜有りの TEG である。図 3.3-1 に測定結果を比較して示す。順方向透過特性(S21)の絶対値は、50GHz で 1dB 弱ポリイミド 薄膜有りの方が小さいが、上述の電極形状の場合と比較してその差は小さい。次に、ポリイミド 薄膜無しの実測データを元にして図 3.3-1 の (f) の等価回路でポリイミド薄膜有りの特性になるよ

うに各定数を求めた。図中に記述するように数 fF 以下で、かつ各 S パラメータ、特に S21 の絶対値に関してもこの等価回路を用いることで良く一致したため、ポリイミド薄膜の誘電体損の影響はほとんど無視できると考える。

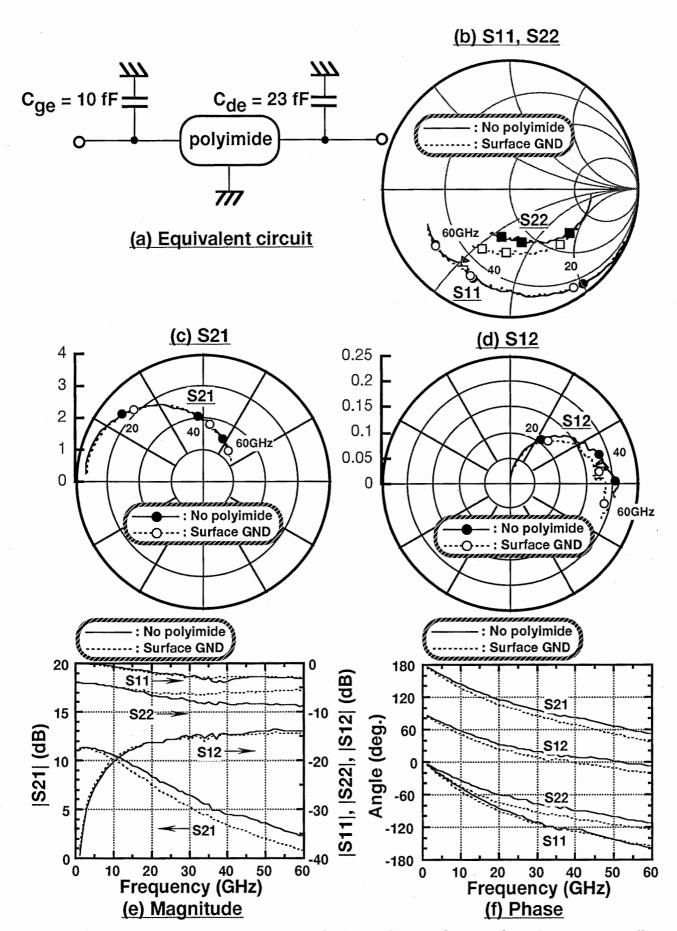

次に上部接地導体の影響について述べる。図 3.3-2 の (a) で示すように、トランジスタ上部にポリイミド薄膜を介して接地導体が有ると、入出力(ゲート、ドレイン)電極と接地間には容量が発生する(各々 Cge, Cde )。この容量の見積もりには HP-Momentum 使用し、単なる平行平板の面積計算ではなく斜め方向の電界も考慮して求め、 Cge, Cde は各々 10, 23fF となった。この結果とポリイミド薄膜有りの実測データを用いて、 (a) で示す回路の S パラメータを計算、図 3.3-2 (b)~(f) にポリイミド無しの実測データと比較して示す。絶対値では順方向透過特性(S21)と出力反射特性(S22)が、位相回りでは入力側の反射特性を除いて全てに差が見られる。図 3.3-1-(d) で示すポリイミド薄膜有りの場合と比較して、 S21 の絶対値が高周波側で大きく劣化して見えるのは、 Cde による S22 の変化、即ち出力リターンロスの劣化の影響が大きいと考える。

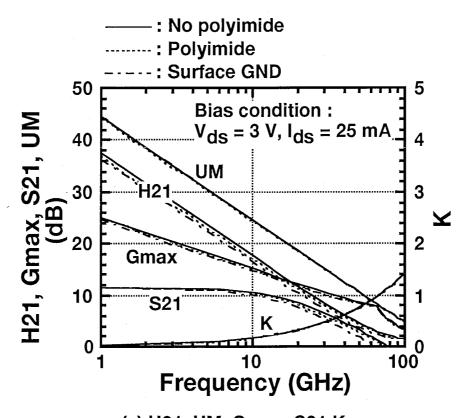

図 3.3-3 にポリイミド薄膜の有無、及び上部接地導体有りの場合の性能指数を比較して示す。 (b) で示すように、fmax には差は見られず、これはポリイミド薄膜の誘電体損を無視できるため と考える。また、ft は順に小さくなっている。

Fig.3.1-1 S-parameter probing configuration.

Fig. 3.1-2 Effect of open-stub (CPW [ 30  $\mu$  m ]).

Fig. 3.1-3 Angle of CPW (10  $\mu$  m).

Fig. 3.2-1 Frequency characteristics of transistors (layout).

Fig. 3.2-2 Small-signal equivalent model of transistor.

Table 3.2 Fitting results of transistors.

| Layout | C <sub>gs</sub><br>(fF) | C <sub>ds</sub><br>(fF) | C <sub>dg</sub><br>(fF) | L <sub>g</sub><br>(pH) | L <sub>d</sub> | L <sub>s</sub><br>(pH) |

|--------|-------------------------|-------------------------|-------------------------|------------------------|----------------|------------------------|

| U      | 79.7                    | 21.2                    | 20.9                    | 21.3                   | 24.1           | 5.0                    |

| Т      | 89.4                    | 34.4                    | 20.3                    | 37.7                   | 32.5           | 4.8                    |

Fig. 3.2-3 Quality factors of transistors.

Fig. 3.3-1 Frequency characteristics of transistors (polyimide).

Fig. 3.3-2 Frequency characteristics of transistors (surface ground).

Fig. 3.3-3 Quality factors of transistors.

写真3-1 U型電極配置

写真3-2 T型電極配置

#### 4 ミリ波帯平衡型増幅器

上記薄膜伝送線路、及び積層化方向性結合器を用いたミリ波帯平衡型増幅器の回路構成と試作結果について述べる[14]-[16]。

#### 4.1 回路構成

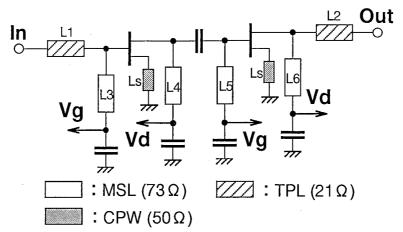

図 4.1-1 に平衡型増幅器に用いた単位増幅器の回路構成を示す。また、表 4.1 に各線路についてまとめる。単位増幅器は 2 段構成で、 DC カットとバイパスコンデンサには MIM キャパシタを用いた。また、入出力の整合には、特性インピーダンス  $21\Omega$  のトリプレート線路を用いている。これはトランジスタの低インピーダンス性を利用して広帯域な利得平坦性を得るためで、従来の MMIC では困難であったが薄膜伝送線路では容易に適用できる。また、用いたトランジスタのゲート幅は  $100\mu$ m で、ソースにはコプレナー線路で形成する線路を接続し、負帰還による若干の安定化を図っている。尚、トランジスタ前後の引出し線路を極力短くし、低インピーダンス線路までの位相回りを抑えて帯域の高周波化を図った。さらに 3 項で述べた上部ポリイミド薄膜による利得劣化を防ぐために、 MMIC 作製の最終工程でトランジスタ上部のポリイミド薄膜のみ除去した。バイアス回路には特性インピーダンス  $73\Omega$  のマイクロストリップ線路を用い、若干の整合機能を持たせている。

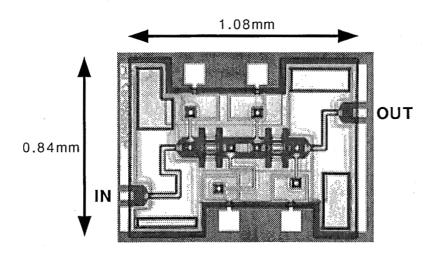

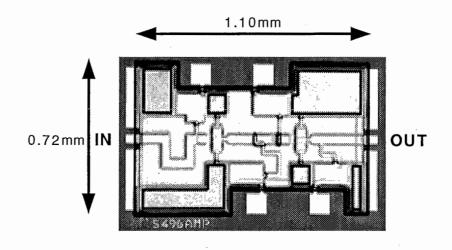

設計上の取り扱いで問題となるのは、異層配線間のヴィアホールを含む変換部である。今回は全てヴィアホールの高さ分を線路長に付加することで処理した。また、段間のDCカットコンデンサはコプレナー線路の中心導体に下層メタルを付加して形成し、計算では集中定数の容量と線路の直列接続とした。写真4-1に単位増幅器の外観写真を示す。

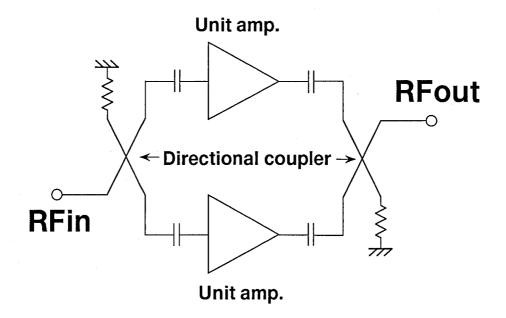

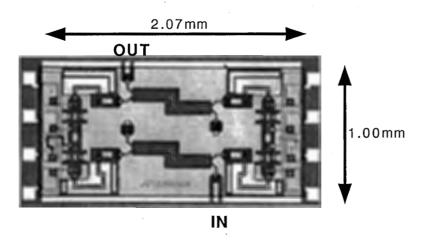

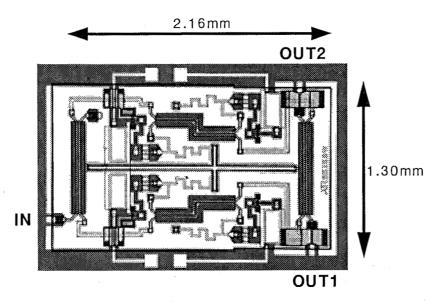

この単位増幅器と上述の積層化方向性結合器 (Normal type, fo=50GHz)を各々2個用いて図 4.1-2 で示す構成の平衡型増幅器を試作した。写真 4-2 に平衡型増幅器の外観写真を示す。

## 4.2 試作結果

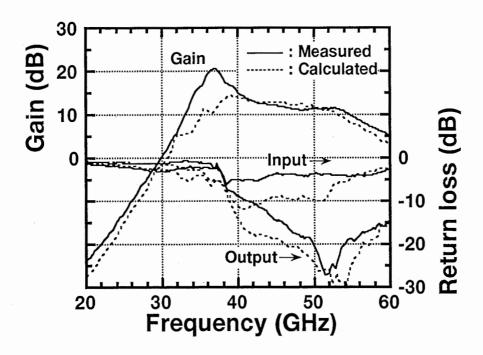

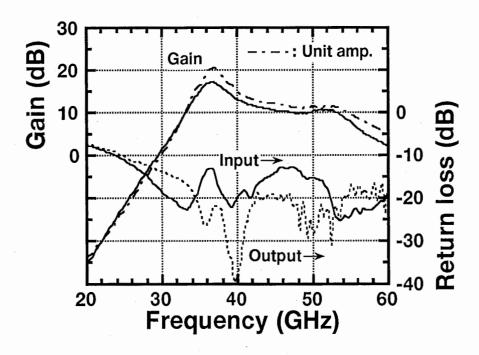

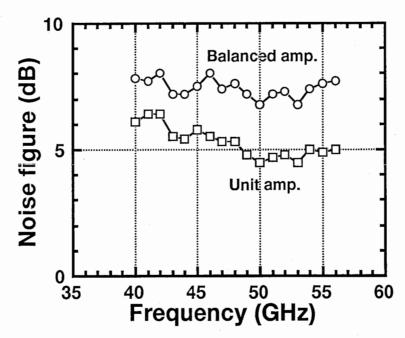

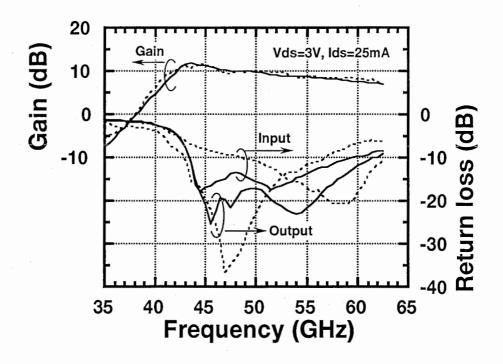

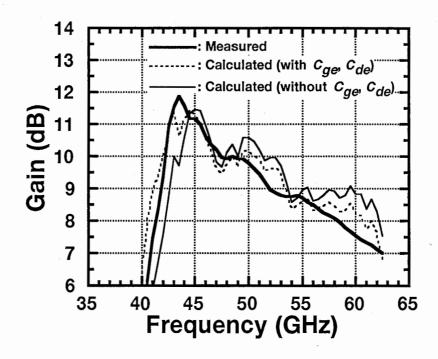

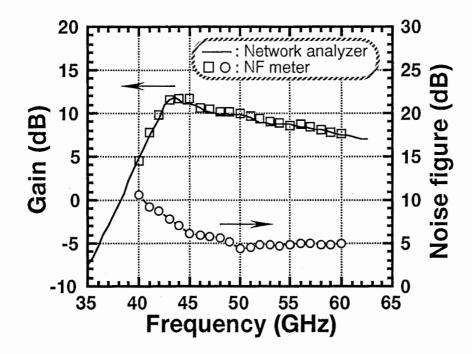

平衡型増幅器、及び同時に試作した単位増幅器をオンウェハで評価した。図 4.2-1 に単位増幅器の利得と入出力反射特性を計算結果と比較して示す。実測結果と計算結果は比較的一致しているが、上述のヴィアホールの取り扱いを 3 次元の電磁界解析で厳密に行なう必要が有ると考える。次に平衡型増幅器の利得と入出力反射特性を図 4.2-2 に示す。同図には比較のため単位増幅器の利得も併せて示す。帯域 33~53 GHz において、平衡型増幅器の利得は 10~17dB、リターンロスは入出力共に 13dB 以上が得られた。利得は約 2dB 単位増幅器と比べて小さく、その内訳は単位増幅器前後の方向性結合器と DC カットコンデンサの損失である。また、図 4.2-3 に示すように雑音指数は 40~56 GHz で 8dB 以下であった。

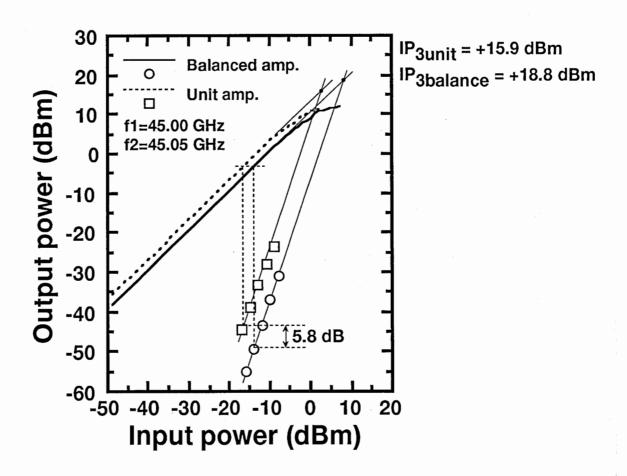

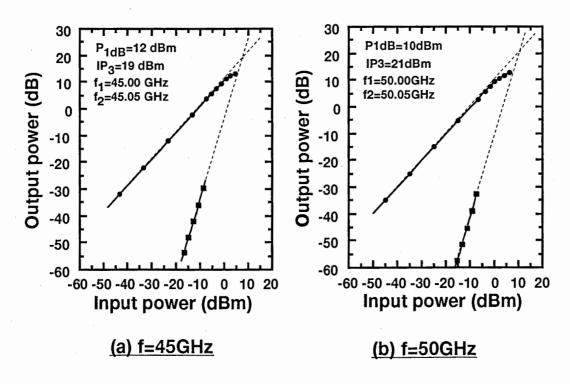

図 4.2-4 に平衡型増幅器と単位増幅器の入出力特性を同時に示す。評価周波数は 45GHz で、3 次相互変調歪は 50MHz オフセットで行った。飽和出力電力は平衡型、及び単位増幅器で、各々約 13dBm、11dBm であった。方向性結合器等が無損失であると飽和出力電力の改善は 3dB が期待できるが、先に述べた約 2dB の損失により、結果的に 2dB の改善となった [19]。また、同電力出力時において約 6dB の 3 次相互変調歪の改善が得られている。尚、 3 次インタセプトポイントは平衡型、及び単位増幅器で、各々 +18.8dBm、及び +15.9dBm であった。

## 4.3 まとめ

多層化 MMIC をミリ波帯能動回路に初めて適用し、その特徴を活かすことで広帯域平衡型 増幅器を実現した。

以下にその主要特性をまとめる。

帯域: 33~53GHz 利得: 10~17dB リターンロス: 13dB以上

雜音指数: 8dB以下 (40~56GHz) 飽和出力: + 13dBm (@ 45GHz)

3 次インタセプトポイント: + 18.8dBm (@ 45GHz, 50MHz オフセット)

Fig. 4.1-1 Circuit diagram of unit amplifier.

Table 4.1 Transmission lines in unit amplifier.

|                 | Line<br>type       | Line            | Characteristics    | Line      | Electrical          |

|-----------------|--------------------|-----------------|--------------------|-----------|---------------------|

| No.             |                    | width impedance |                    | length    | length ( $\theta$ ) |

|                 |                    | $(\mu m)$       | (Ω)                | $(\mu m)$ | @50GHz              |

| L1              | Triplate line      | 40              | 01.1               | 500       | 57.7                |

| L2              | $(T=10 \mu m)$     | 18              | 21.1               | 290       | 33.5                |

| L3              |                    | 10              |                    | 90        | 8.9                 |

| <u>L4</u><br>L5 | Microstrip<br>line |                 | 73.1               | 400       | 39.5                |

| L5              | (T=10 μ m)         |                 | 73.1               | 90        | 8.9                 |

| L6              |                    |                 |                    | 90        | 8.9                 |

| Ls              | CPW                | Wid             | th / Gap = 56 / 27 | 30        |                     |

Fig. 4.1-2 Circuit diagram of balanced amplifier.

Fig. 4.2-1 Measured and calculated frequency characteristics of fabricated unit amplifier.

Fig. 4.2-2 Measured frequency characteristics of fabricated balanced amplifier (as compared with gain of unit amplifier).

Fig. 4.2-3 Measured noise figure.

Fig. 4.2-4 Output power of the fundamental and third-order intermodulation products as a function of input power.

写真4-1 単位増幅器

写真4-2 平衡型増幅器

## **5 SPDT** スイッチ

積層化方向性結合器を用いた他の回路として、ミリ波帯高アイソレーション SPDT スイッチ (Single-Pole-Double-Throw) を試作した。

## 5.1 回路構成

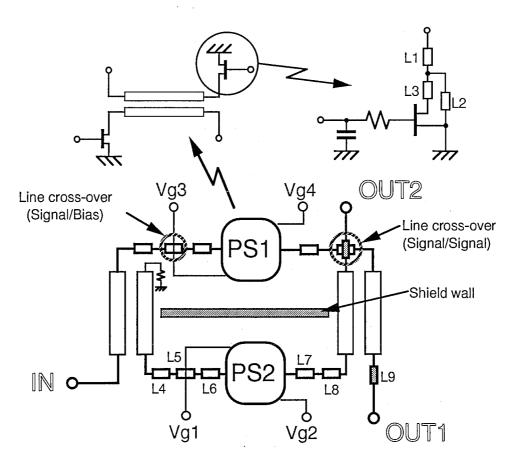

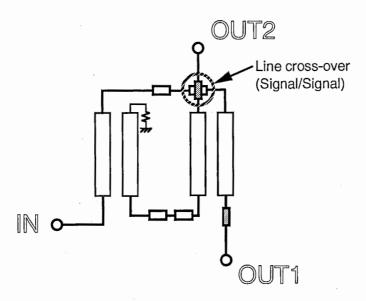

図 5.1-1 に SPDT スイッチの回路構成を示す。方向性結合器で 2 分配した信号を  $0/\pi$  反転移相器 (Phase shifter) でその位相を制御した後、再度信号を合成する事で切り替えスイッチを構成する。移相器は、方向性結合器のアイソレーションポートに可変インピーダンス素子を接続することで構成する。今回はその可変インピーダンス素子として、トランジスタ (Wg= $100\mu m$ ) のドレイン端を接続した。トランジスタのゲート側には信号漏洩防止のための抵抗(数  $k\Omega$ )とバイパスコンデンサを接続し、ドレイン側には伝送線路による共振回路 (L1, L2, L3) を付加している。これはトランジスタの ON/OFF 時の特性が理想的なショート / オープンとなっていないことを補正するためのもので、 ON 抵抗による移相器の通過特性劣化を緩和し、且つ、ドレイン端での反射位相が ON/OFF 時で反転するように設計している。帯域は狭くなるが、同相 / 逆相設定時の移相器の挿入損失を平均化すると共に所望の帯域において位相反転させ、結果的には SPDTの経路による挿入損失差を無くしている。方向性結合器は Normal type、中心周波数  $50 \, {\rm GHz}$  の積層化方向性結合器を用いた。また、表 5.1-1 に各線路についてまとめる。

次に経路切り替えのバイアス条件を表 5.1-2 に示す。移相器の 2 個のトランジスタには同じ電圧を印加し、 2 個の移相器に同じバイアスを印加する場合には同相となり、各経路を通過した信号は OUT2 で同相合成され IN-OUT2 間が ON となる。逆にバイアスを ON/OFF いずれかに異なるように設定すると、 OUT1 で同相合成され IN-OUT1 間が ON となる。

また、本スイッチのレイアウト上の特徴として、立体的に交差する線路をそのストリップ導体間に接地導体を介して構成することで線路間の結合を、さらに信号分配後の経路間に接地導体によるシールド壁を配置して、経路間の結合を防止している。

## 5.2 試作結果

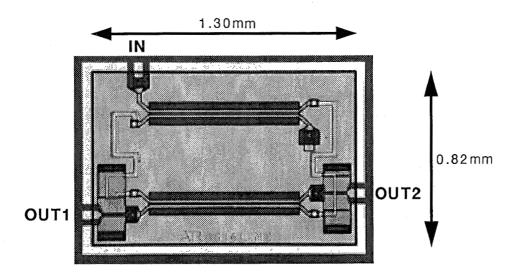

### **5.2.1** SPDT スイッチ

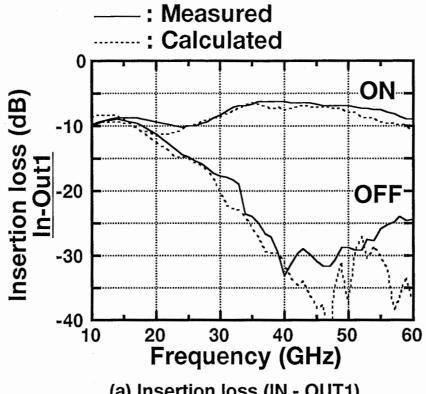

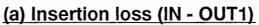

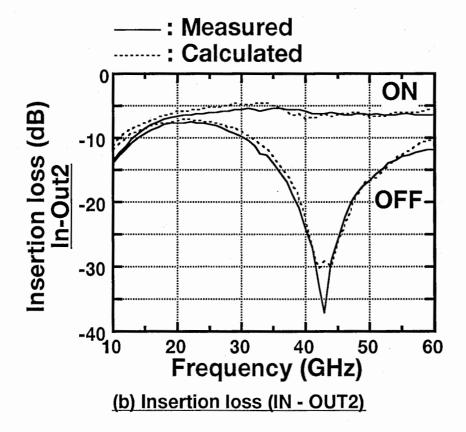

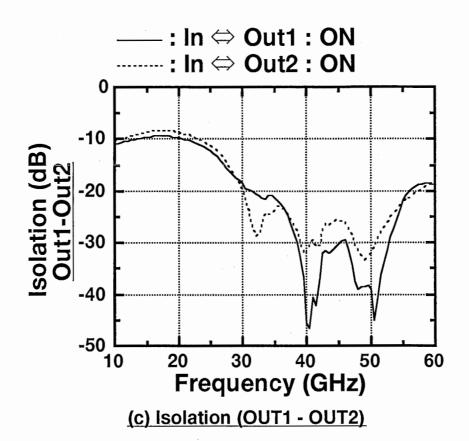

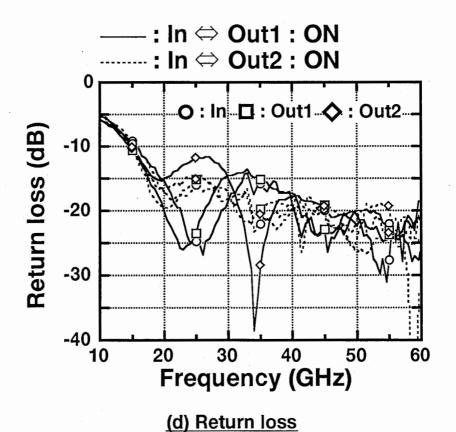

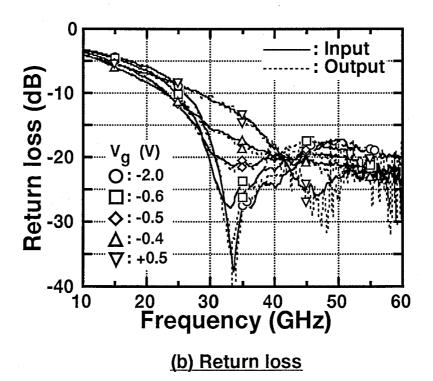

まず、SPDT 特性について述べる。図 5.2-1 に SPDT スイッチの小信号特性を示す。尚、移相器のトランジスタに印加するゲートバイアスは、ON 時で+0.5V、OFF 時で -2V とした。 (a) は経路 IN-OUT1 の通過特性を示し、 $35\sim50$  GHz で ON/OFF 時の挿入損失は各々 7dB 以下、25 dB 以上、 $38\sim45$  GHz で各々 6dB 以下、28 dB 以上が得られた。 (b) は経路 IN-OUT2 の通過特性を示し、 $40\sim45$  GHz で ON/OFF 時の挿入損失は各々 6dB 以下、25 dB 以上が得られた。経路 IN-OUT1 と比べて帯域が狭くなっているのは移相器のトランジスタに付加した共振回路の影響である。 (c) は OUT1-OUT2 間のアイソレーション特性で  $38\sim53$  GHz で 30 dB 以上が得られている。 (d) は各入出力端の反射特性を示す。どの経路を ON/OFF した場合でも 35 GHz 以上の帯域でで 15 dB のリターンロスが得られている。

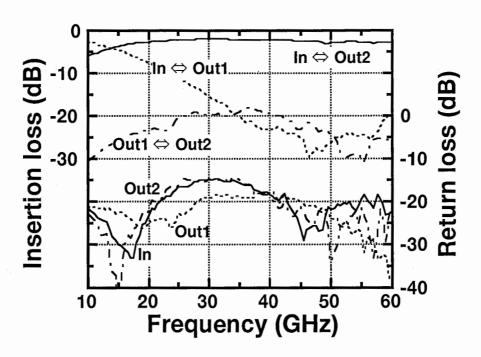

当初の設計では中心周波数を  $50 \mathrm{GHz}$  に設定していたが、試作後のトランジスタ特性の違いから約  $43 \mathrm{GHz}$  が中心となった。また、(a)-(c) に示す計算結果は、同ウェハ内のトランジスタ TEG を評価して得た  $\mathrm{S}$  パラメータを用いている。この場合には、両者良く一致している。また、  $\mathrm{SPDT}$  スイッチから 2 個の移相器を取り除き、経路特性を評価するための TEG を作製した。その特性を図 5.2-2 に、その回路図と共に示す。この場合  $\mathrm{IN}$ -OUT2 間が  $\mathrm{ON}$  経路となり、その挿入損失

は  $20\sim60\,\mathrm{GHz}$  の広帯域で  $3\mathrm{dB}$  以下で、これは 2 個の方向性結合器の損失と線路交差を含む引き回し線路の損失によるものと考える。また、IN-OUT1 間の OFF 経路の挿入損失は  $35\sim50\,\mathrm{GHz}$  で  $18\mathrm{dB}$  以上と、図 5.2-1-(a) で示した SPDT スイッチの OFF 特性を下回っている。さらに OUT1-OUT2 間のアイソレーション特性についても同様で、この SPDT スイッチにおける特性改善はレイアウト上、特に接地導体のシールド壁の効果と考えられる。

尚、SPDT スイッチ、及び経路 TEG の外観を写真 5-1, 2 に各々示す。

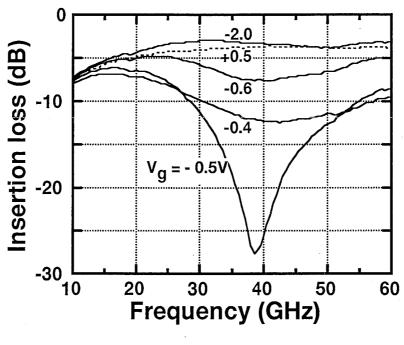

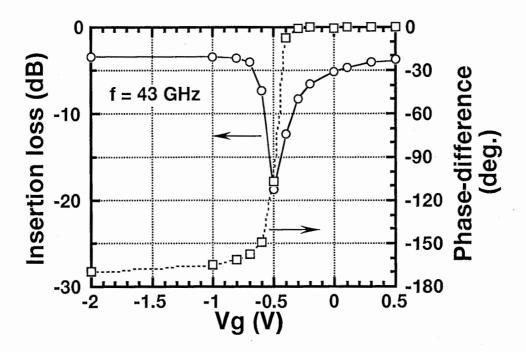

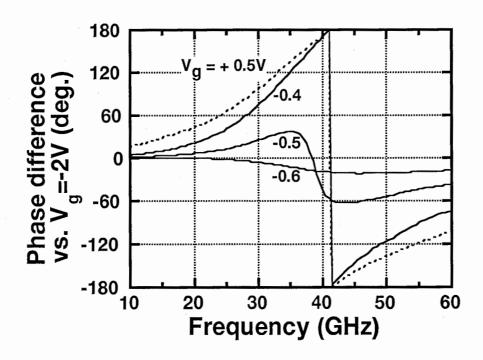

#### 5.2.2 移相器

本構成の移相器は SPST スイッチ (Single-Pole-Single-Throw)、及び減衰器としても機能する。まず、これらの機能の特性についてを述べる。図 5.2-3-(a) に挿入損失特性を (b) に入出力端の反射特性を示す。ゲートバイアス -2V/-0.5V でスイッチは ON/OFF し、挿入損失は 37~40GHz と帯域は狭いが各々約 3.5/25dB である。挿入損失はバイアスを調整することで連続的に変えることができる。尚、入出力端のリターンロスは、ゲートバイアスに係わらず 15dB 以上が得られている。

次に移相器としての特性について述べる。図 5.2-4-(a) に SPDT スイッチの中心周波数である  $43 \mathrm{GHz}$  での挿入損失と位相変化量のゲートバイアス依存性を示す。ゲートバイアス  $-2/+0.5\mathrm{V}$  時で挿入損失は共に約 3.5dB、位相変化量は約  $170^\circ$  が得られている。同図 (b) にはゲートバイアス  $-2\mathrm{V}$  時の位相を基準にしたバイアスによる変化量の周波数特性を示す。約  $42\mathrm{GHz}$  で位相反転している。 SPDT スイッチの中心周波数  $43\mathrm{GHz}$  との差は今の所分かっていない。

尚、移相器の外観を写真 5-3 に示す。

#### 5.2.3 入出特性

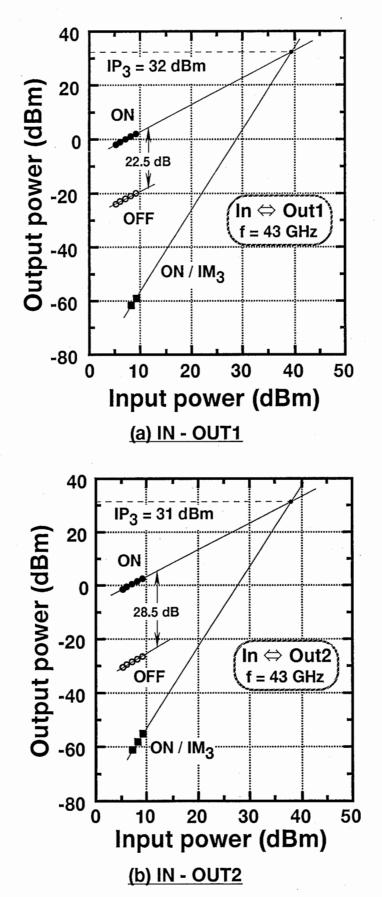

周波数  $43 \mathrm{GHz}$  において基本波の入出特性と  $5 \mathrm{MHz}$  オフセットの 3 次相互変調歪特性を評価した。図 5.2-5-(a) に経路 IN-OUT1 の, (b) に経路 IN-OUT2 の ON/OFF 時の基本波、及び 3 次相互変調歪に関しては ON 時のみの結果を示す。測定に用いた増幅器の飽和出力の制限で約+  $10 \mathrm{dBm}$  までしか入力できなかったため、基本波については直線性の劣化は観察できなかった。各々の経路における 3 次インタセプトポイントは +32,  $+31 \mathrm{dBm}$  で、比較するデータは無いがこの周波数域では良好な結果と考える。

### 5.3 まとめ

本構成のSPDTスイッチでは、入力信号が2個の方向性結合器で分配され、結果的に入力電力の1/4がトランジスタのドレインに入射することになる。そのため、他の構成のスイッチ回路と比較して良好な入出力特性が期待できる。また、どの経路をON/OFFしても各入出端のリターンロスは方向性結合器の特性で決まり良好である。さらに多層化MMICの特徴を活かしてレイアウトをすることで経路間の結合を防止し、良好なアイソレーション特性が得られることを示した。

以下にその主要特性をまとめる。

帯域: 40~45GHz 挿入損失(両経路): 6dB以下(ON) 25dB以上(OFF) 出力間アイソレーション: 30dB以上 リターンロス(両経路,全入出端): 15dB以上 3次インタセプトポイント(両経路): +31dBm以上(@43GHz,5MHzオフセット)

Fig. 5.1-1 Circuit diagram of SPDT switch.

Table 5.1-1 Transmission lines in SPDT switch.

|           | Lino                                 | Line      | Characteristics | Line      |

|-----------|--------------------------------------|-----------|-----------------|-----------|

| No.       | Line                                 | width     | impedance       | length    |

|           | type                                 | $(\mu m)$ | (Ω)             | $(\mu m)$ |

| <u>L1</u> |                                      | 10        | 73.1            | 230       |

| L2        |                                      |           |                 | 540       |

| L3        | Microstrip<br>line<br>(T=10 $\mu$ m) |           |                 | 50        |

| L4        |                                      | 20        | 50.9            | 290       |

| L6        |                                      |           |                 | 190       |

| L7        |                                      |           |                 | 660       |

| L5        | Microstrip                           | 10        | 50.0            | 155       |

| L8        | line(T=5 μm)                         |           |                 | 300       |

| L9        | Inverted line<br>(T=5 μm)            | 6         | 41.7            | 110       |

Table 5.1-2 Bias condition of SPDT switch.

| Vg1/2     | Vg3/4 | PS1/PS2      | Output-port |

|-----------|-------|--------------|-------------|

| off(-2V)  | off   | in phase     | OUT2        |

| on(+0.5V) | on    | in phase     | OUT2        |

| off       | on    | out of phase | OUT1        |

| on        | off   | out of phase | OUT1        |

Fig. 5.2-1 Measured and calculated performance of fabricated SPDT switch.

Fig. 5.2-1 (Cont' d) Measured and calculated performance of fabricated SPDT switch.

(a) Circuit diagram

(b) Measured frequency characteristics

Fig. 5.2-2 Measured performance of signal path -TEG.

Fig. 5.2-3 Measured performance of phase shifter (as SPST or attenuator).

(a) Insertion loss and phase difference as afunction of control bias.

(b) Frequency characteristics of phase difference.

Fig. 5.2-4 Measured performance of phase shifter.

Fig. 5.2-5 Output power of the fundamental and third-order intermodulation products as a function of input power.

写真5-1 SPDT スイッチ

写真5-2 経路TEG

写真5-3 移相器

### 6 スタック **IC**

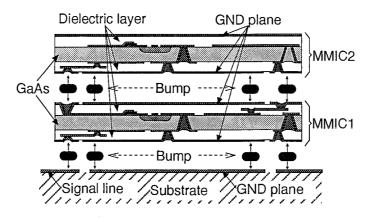

MMIC の超小型化を目的として多層化 MMIC 技術の検討がなされてきたが、これまでは半導体基板上に受動回路を積層するにとどまり、能動回路の積層はなされていない。 MMIC チップとして能動回路を積層するには、半導体基板上に形成した誘電体層のさらに上に半導体による動作層を形成しなければならず、現状技術では困難である。そこで近年、マイクロ波・ミリ波においても適用の試みがなされているバンプ実装技術 [20] を用いて、複数個の MMIC チップを縦方向に積層するスタック IC(Stacked Integrated Circuits) を提案する。また、本 IC に適用できる構造のミリ波帯増幅器を試作したので、その結果について述べる [17]—[18]。

### 6.1 構造と特徴

図 6.1-1 にスタック IC の構造イメージを示す。複数個の MMIC チップをバンプ実装により 縦方向に積層する。本構造の実装を行なうには、チップ間、或いはチップ・基板間の電磁的結合 を除去するため接地導体で遮蔽する必要が有る。このような構造は、2.2 の薄膜伝送線路で述べた表面に接地導体を有する逆マイクロストリップ線路やトリプレート線路を用いて実現することができる。特に2.2 項で述べたように、逆マイクロストリップ線路はコプレナー線路とほぼ同等の波長短縮率、伝送損失を有しており適当であると考える。

次にその特徴について述べる。

(1) ワイヤやリボンによるボンディングと比べてバンプによる接続では、接続部での寄生成分の低減が可能、特に個々の MMIC チップは遮蔽構造となっているので、通常のバンプ実装と比較してもチップ・基板間、チップ・チップ間距離を極端に短くできる。従って実装での特性劣化を考慮することなくモジュール設計ができ、自由度も大きいため超小型・高機能 MMIC モジュールが可能となる。

以降は個々の MMIC について:

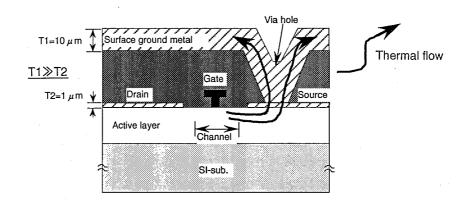

- (2) 図 6.1-2-(a) に示すように、トランジスタ等の能動素子近傍に設けた厚みのあるビアホールを介して表面の接地導体と素子の接地とを接続することで、素子動作部で発生する熱を効果的に放散させることが可能となる [21]。

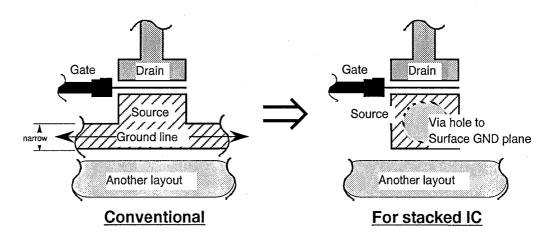

- (3) 図 6.1-2-(b) に示すように、トランジスタ等の能動素子の接地を MMIC チップ内の接地 導体に接続する際、ビアホールを介して表面の接地導体と接続することができ、隣接して配置する回路パターンの制約を受けないためサイズを大きくせずに完全な接地が可能となる。

## 6.2 試作 MMIC

スタック IC の実現性を確認するため、MMIC 単体について表面が接地導体で覆われている MMIC を試作した。

#### 6.2.1 回路構成

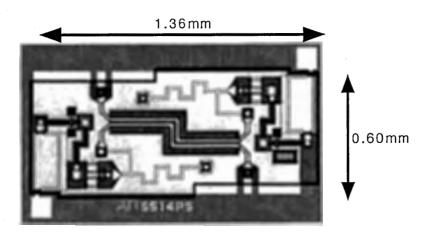

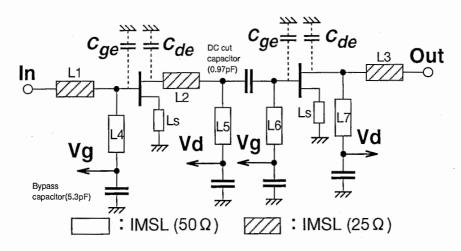

試作した回路はミリ波帯で動作する 2 段増幅器で、図 6.2-1 にその回路構成を示す。伝送線路は全て逆マイクロストリップ線路で構成した。設計は 3.3 で述べたトランジスタ上部接地導体の影響を考慮して行なった。入出力、及び段間の整合回路には特性インピーダンス  $25\Omega$  の、バイアス回路、及び安定化のための負帰還用線路には  $50\Omega$  の逆マイクロストリップ線路を用いた。整合回路に低インピーダンス線路を用いているのは、 4 項で述べた平衡型増幅器と同様に広帯域で利得平坦性を得るためである。尚、用いたトランジスタのゲート幅は  $100\mu$ m である。表 6.2 に各伝送線路についてまとめる。

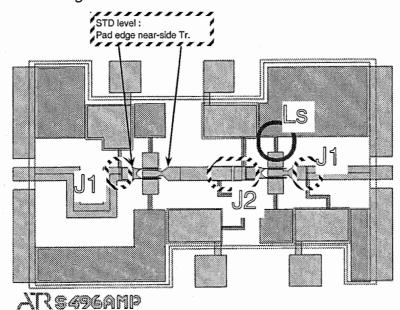

設計上の取り扱いは先に述べた平衡型増幅器と比較して、トランジスタの接地以外にはヴィアホールを全く使用していない点で問題は少ない。只、設計精度向上の目的で、図 6.2-2 のレイアウト図に J1、J2、及び Ls で示す不連続部の特性については、HP-Momentun を用いて求めた。また、段間の DC カットコンデンサは、2.2 の薄膜伝送線路で述べた MIM 容量を併せ持つ構造の逆マイクロストリップ線路 (図 2.2-1-(4)) を用いた。尚、トランジスタ TEG のプロービングパッド幅 ( $42\mu$ m) とトランジスタ前後に配置する伝送線路の幅を同一にすることで、トランジスタの基準面までを単一の線路と扱える。

写真6に本増幅器の外観写真を示す。尚、入出力、及びバイアス電極は評価の容易さから GaAs 基板上に配置した。

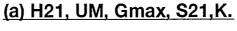

#### 6.2.2 試作結果

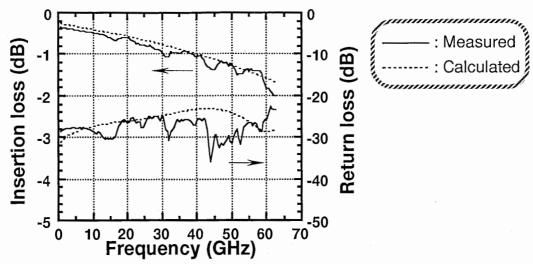

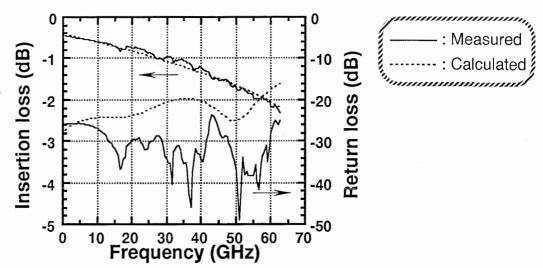

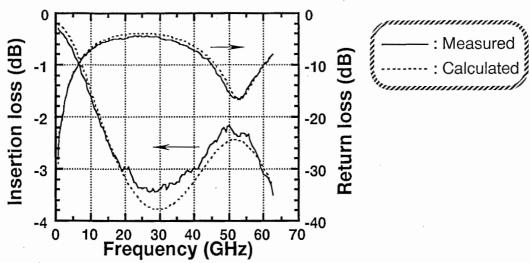

試作 MMIC をオンウェハ評価した。図 6.2-3 に小信号利得、及び反射特性の周波依存性を示す。 42~56GHz において、利得 10±3dB、リターンロスは入出力共に 10dB 以上が得られた。尚、測定結果と計算結果は良く一致している。また、トランジスタ上部接地導体がどの程度、増幅器の帯域に影響しているかを調べるため、その影響を考慮しない場合の利得の計算結果も含めて図 6.2-4 に示す。立ち上がりにおける帯域のシフトは 2GHz 以下、帯域内の利得減少は 0.5dB 以内であり、本回路のような広帯域設計の回路では問題にはならないと考える。

次に雑音特性を図 6.2-5 に示す。 50~60GHz において 5dB 以下が得られている。また、雑音測定 (by NF meter) で同時に得られる利得は、先に述べた小信号利得 (by Network analyzer) と一致している。

図 6.2-6 に周波数は 45、及び 50GHz における入出力特性を示す。 3 次相互変調歪は 50MHz オフセットで行った。 1dB 利得圧縮点出力電力( P1dB )は各々 + 12、 + 10dBm、 3 次インタセプトポイント( IP3 )は各々 + 19、 + 21dBm であった。

#### 6.3 まとめ

MMIC の超小型・高機能化に対する究極の実装スタイルと考えられるスタック IC を提案し、本 IC に適用できる構造のミリ波帯増幅器を多層化 MMIC の特徴を活かして試作し、その結果について述べた。

以下にその主要特性をまとめる。

帯域: 42~56GHz 利得: 10±3dB リターンロス: 10dB以上

雜音指数: 5dB以下(50~60GHz)

1dB 利得圧縮点出力電力:+ 12dBm(@ 45GHz)、+ 10dBm(@ 50GHz)

3 次インタセプトポイント: + 19dBm(@ 45GHz)、+ 21dBm(@ 50GHz)

Fig. 6.1-1 Cross-sectional view of stacked integrated circuits.

# (a) Thermal effect

(b) Ground line layout

Fig. 6.1-2 Features of multilayer MMIC for stacked IC.

Fig. 6.2-1 Circuit diagram of fabricated amplifier.

Table 6.2 Transmission lines of amplifier.

|     | Line      | Characteristics | Line      | Electrical          |

|-----|-----------|-----------------|-----------|---------------------|

| No. | width     | impedance       | length    | length ( $\theta$ ) |

|     | $(\mu m)$ | (Ω)             | $(\mu m)$ | @50GHz              |

| L1  |           |                 | 501       | 76.5                |

| L2  | 42        | 25.6            | 165       | 22.9                |

| L3  |           |                 | 200       | 27.7                |

| L4  |           |                 | 60        | 9.2                 |

| L5  |           |                 | 300       | 45.8                |

| L6  | 10        | 50.7            | 94        | 14.4                |

| L7  |           |                 | 160       | 24.4                |

| Ls  |           |                 | 50        | 7.6                 |

\* J1, J2, Ls,  $C_{ge}$  (=10fF) ,  $C_{de}$  (=23fF) : calculated by HP-Momentum

Fig. 6.2-2 Schematic layout of amplifier.

Fig. 6.2-3 Measured and calculated frequency characteristics of fabricated amplifier.

Fig. 6.2-4 Measured and calculated frequency characteristics of fabricated amplifier (gain).

Fig. 6.2-5 Measured noise figure and gain (by NF meter).

Fig. 6.2-6 Output power of the fundamental and third-order intermodulation products as a function of input power.

写真6 逆マイクロストリップ線路で構成した増幅器

### 7 あとがき

本報告の前半では、ミリ波帯多層化 MMIC を設計・試作する上で必要と考えられる情報について述べた。基本となる薄膜伝送線路には様々な構造が考えられ、これらを組み合わせて用いることで配線の自由度、即ち設計性の向上が図れる。また、伝送損失の点でもコプレナー線路と比べて遜色無く、さらに有限要素法による解析結果を用いて精度良く線路設計できることを示した。次に積層化方向性結合器については、50 GHz 帯で良好な特性が得られ、設計性も良好であった。また、能動回路に用いるトランジスタの取り扱いに関しては、基準面の設定が重要で有ること、さらに多層化 MMIC に特異な上部誘電体、及び接地導体の特性への影響について述べた。

後半では、これらを元にして設計・試作したミリ波帯平衡型増幅器と SPDT スイッチについて、続いて超小型・高機能化に対する究極の実装スタイルと考えられるスタック IC の提案を行ない、多層化 MMIC を適用することで実現する本 IC に適したミリ波帯増幅器の試作結果について述べた。平衡型増幅器では帯域  $33\sim53 \mathrm{GHz}$  の広帯域で利得  $10\sim17\mathrm{dB}$  が、 SPDT スイッチでは帯域  $40\sim45\mathrm{GHz}$  で両経路共に挿入損失  $6\mathrm{dB}$  以下 (ON 時) /25dB 以上 (OFF 時) が得られた。また、スタック IC に適用できる構造のミリ波帯増幅器では、帯域  $42\sim56\mathrm{GHz}$  で利得  $10\pm3\mathrm{dB}$  が得られた。

1

以上、多層化 MMIC がミリ波帯においても、超小型化・高機能化に有効であることを確認 した。

## 铅锯

本研究を進めるにあたって、直接ご指導頂いた今井伸明主任研究員、ならびに積層化方向性結合器の考案者で、数多くの助言を頂いた馬場清一氏 (元 ATR 光電波通信研究所・現三洋電機(株)) に深謝いたします。また、本研究の遂行にあたり、討論を通じて有益なるご教示を頂いた葉原耕平会長、猪股英行社長、小川英一室長ならびに無線通信第2研究室の皆様に感謝いたします。

## 8 参考文献

## 参考文献

- [1] T. Hiraoka, et al., "Very small wide-band MMIC magic-T's using microstrip lines on a thin dielectric film," *IEEE Trans. Microwave Theory and Tech.*, MTT-37, pp. 1569–1575, 1989.

- [2] H. Nakamoto, et al., "A monolithic, port-interchanged rat-race hybrid using a thin film microstrip line crossover," 19th. European Microwave Conf., pp. 311–316, 1989.

- [3] T. Tokumitsu, et al., "Multilayer MMIC using a  $3\mu m \times 3$ -layer dielectric film structure," *IEEE MTT-S Int. Microwave Symp.*, pp. 1067–1070, 1990.

- [4] 中本 他, "ポリイミドを用いた多層化MMICによる超小型ハイブリッド回路," 信学会技術 研究報告, MW89-141, pp. 59-66, 1990.

- [5] 馬場 他, "多層化MMICによる超小型ハイブリッド回路の構成と特性," 信学会技術研究報告, MW91-109, pp. 1-7, 1991.

- [6] S. Banba, et al., "Multilayer MMIC branch-line hybrid using thin dielectric layers," IEEE Microwave and Guided Wave Lett., Vol. 1, pp. 346–347, 1991.

- [7] 長谷川 他, "V溝MM I C伝送線路を用いたブランチラインハイブリッド," 信学会 9 1年秋 季全国大会, C-100, pp. 2-381.

- [8] S. Banba, et al., "Novel MMIC transmission lines using thin dielectric layers," *IEICE Trans. Electron.*, **E75-C**, pp. 713–720, 1992.

- [9] S. Banba and H. Ogawa, "Small-sized MMIC amplifiers using thin dielectric layers," *IEEE Trans. Microwave Theory and Tech.*, vol. MTT-43, pp. 485–492, Mar. 1995.

- [10] 馬場 他, "多層化MMICによる方向性結合器の構成と特性," 信学会技術研究報告, MW93-91, pp. 1-7, 1993.

- [11] S. Banba and H. Ogawa, "Multilayer MMIC directional couplers using thin dielectric layers," *IEEE Trans. Microwave Theory and Tech.*, vol. MTT-43, pp. 1270–1275, June. 1995.

- [12] 今岡他, "多層構造を用いた Ka 帯 MMIC 平衡型増幅器," 1994 年信学会秋季大会,C-35, 1994.

- [13] 馬場 他, "多層化 MMIC による方向性結合器とミリ波回路への応用," 信学会論文誌,**J77-C-I**, pp. 617-624, 1994.

- [14] T. Imaoka, S. Banba, N. Imai, "A Millimeter-Wave Wideband Balanced Amplifier using Multilayer MMIC Directional Couplers," 25th. European Microwave Conf., pp. 1001–1005, 1995.

- [15] 今岡 他, "多層構造を用いたミリ波帯 MMIC 平衡型増幅器," 1994 年信学会秋季大会,C-35, 1994.

- [16] 今岡 俊一、馬場 清一、今井 伸明, "多層構造を用いたミリ波帯 MMIC 平衡型増幅器," 信学会技術研究報告, **MW95-12**, pp. 13–18, 1995.

- [17] 今岡 俊一、皆川 晃、今井 伸明, "スタック IC に適した多層化 MMIC" 1996 年信学会総合大会,C-44, 1996.

- [18] T. Imaoka, A. Minakawa, N. Imai, "Multilayer MMIC for Stacked Integrated Circuits," 26th. European Microwave Conf., September 1996. (投稿中)

- [19] K. Kurokawa, "Design theory of balanced transistor amplifiers," *Bell System Technical Journal*, pp. 1675–1698, Oct. 1965.

- [20] H. Sakai, Y. Ota, K. Inoue, T. Yoshida, K. Takahashi, S. Fujita and M. Sagawa, "A novel millimeter-wave IC on Si substrate using flip-chip bonding technology," in *Proc. IEEE MTT-S Int. Microwave Symp.*, June 1994, pp. 1763–1766.

- [21] B. Bayraktaroglu, J. Barrette, L. Kehias, C. I. Huang, R. Fitch, R. Neidhard, and R. Scherer, "Very high-power-density CW operation of GaAs/AlGaAs microwave heterojunction bipolar transistors," *IEEE Electron Device Lett.*, vol. 14, pp. 493–495, Oct. 1993.